CPU與RAM的隔閡

CPU與RAM是兩個獨立的硬件,并非集成在一起。所以他們兩個之間一定會存在一個連接的橋梁,這個橋梁的名字叫做內存總線。

內存總線由三部分組成:

地址總線(Address Bus)

用于傳輸內存地址,也就是我們經常看到的0X77F84FAB這種類似的內存地址,一根總線代表一個電信號,一個電信號能傳遞高電平/低電平兩種信息,用二進制表示就是1/0。因此總線數量的多少決定了可以傳遞內存地址的大小,比如你有32根總線,就代表你總線寬度32。2^32=4294967296,等于4GB內存,這就是32位操作系統只支持4G內存的由來。

數據總線(Data Bus)

用于傳輸數據,原理同上,一根總線代表1bit傳輸段位,64根總線就是 64bit=8byte。一次性可以傳輸8byte單位的數據。

控制總線(Control Bus)

用戶傳輸控制信號,比如一根用來"讀信號輸出"的開關,一根"寫信號輸出"的開關。一根"時鐘信號"的開關

更詳細可以參考此文:https://www.cnblogs.com/lmy5215006/p/18469027

CPU Cache

可以看到,假設CPU要讀取1kb的數據,你的數據總線總線只有64根,1024/8=128,你需要來回倒騰128次,才能讀取完畢,這一來二去就加大了內存之間的延遲,為了優化此性能瓶頸,

CPU除了寄存器外臨時存儲數據,還內置了Cache來臨時存儲數據與指令。

游戲神U 9800x3d就是依靠96MB的"巨大L3緩存",來降低了內存延遲,從而在游戲場景默秒全Intel

| 特性 | L1緩存 | L2緩存 | L3緩存 |

|---|

| 速度 | 1-2納秒 | 約10納秒 | 約30納秒 |

| 容量 | 幾十KB到幾百KB | 幾百KB到幾MB | 幾MB到幾十MB |

| 位置 | 集成在 CPU 核心內部 | 每個核心獨立擁有(位于核心附近) | 多核共享(位于 CPU 芯片內) |

| 緩存一致性 | 每個核心獨立,與L3主從同步 | 每個核心獨立,與L1/L3主從同步 | 多核共享 |

| 場景 | 需要立即執行的指令與高頻訪問的數據 | 稍低頻但重復訪問的數據 | 跨核心共享數據、大吞吐量計算 |

what is CacheLine?

CacheLine是CPU緩存中最小數據單元,當CPU從內存中讀取數據時,會一次性加載64byte的數據,而不是只加載特定數據,即使只想讀取1bit數據,也會加載64byte數據。這么做是因為,大多數情況下,數據都是順序讀取的,因此提前加載數據有利于減少延遲。

眼見為實

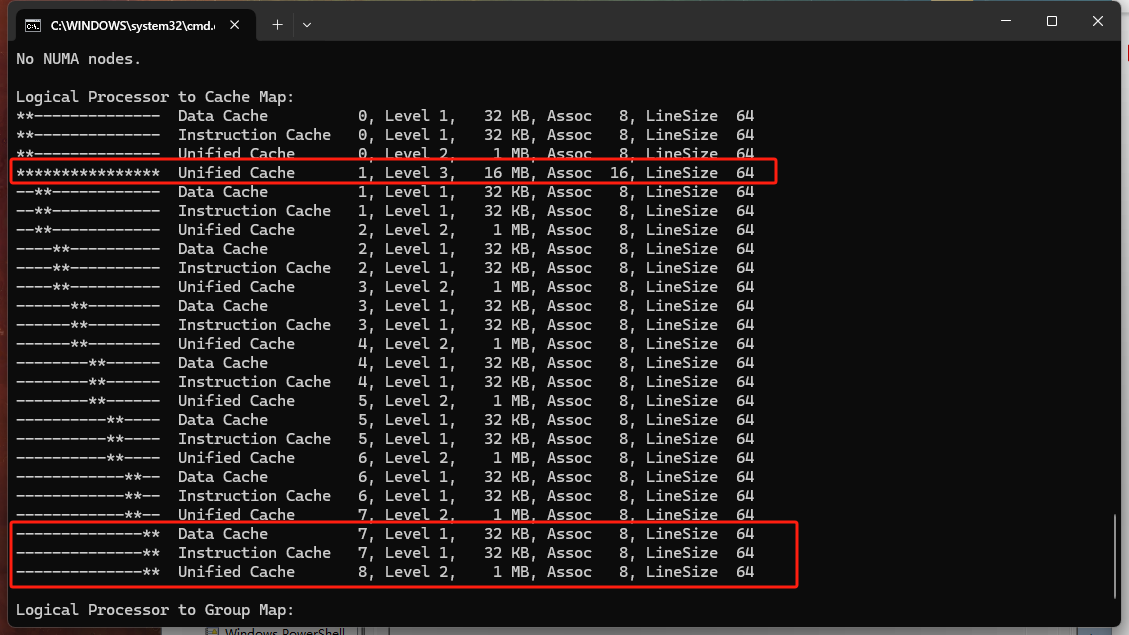

使用Coreinfo 來觀察CPU

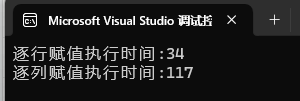

C#代碼如何影響CPU緩存速度?

internal class Program

{

static void Main(string[] args)

{

Stopwatch sw = new Stopwatch();

sw.Start();

Rows();

sw.Stop();

Console.WriteLine($"逐行賦值執行時間:{sw.ElapsedMilliseconds}");

sw.Restart();

Columns();

sw.Stop();

Console.WriteLine($"逐列賦值執行時間:{sw.ElapsedMilliseconds}");

}

static void Rows()

{

int[,] tab = new int[5000, 5000];

for (int i = 0; i < 5000; i++)

{

for (int j = 0; j < 5000; j++)

{

tab[i, j] = 1;

}

}

}

static void Columns()

{

{

int[,] tab = new int[5000, 5000];

for (int i = 0; i < 5000; i++)

{

for (int j = 0; j < 5000; j++)

{

tab[j, i] = 1;

}

}

}

}

}

可以看到,非線性的數據檢索帶來了嚴重的性能問題,應當盡量避免對內存的非順序訪問。

?轉自https://www.cnblogs.com/lmy5215006/p/18916344

該文章在 2025/6/11 9:07:47 編輯過